|

ͼ��23�� Step1: ��VDD����ߵ�ѹ������tester�ĵ�ѹԴ�趨һ��ǯ�Ƶ�������ֹ������������Ի��� Step2: ��оƬ�������ϵ������ض���pattern,�ȴ�5~10ms��Step3: ��������VDD�ϵĵ���������datasheet�еı�ʶ�趨limit������limit��ʾ��Ʒ��

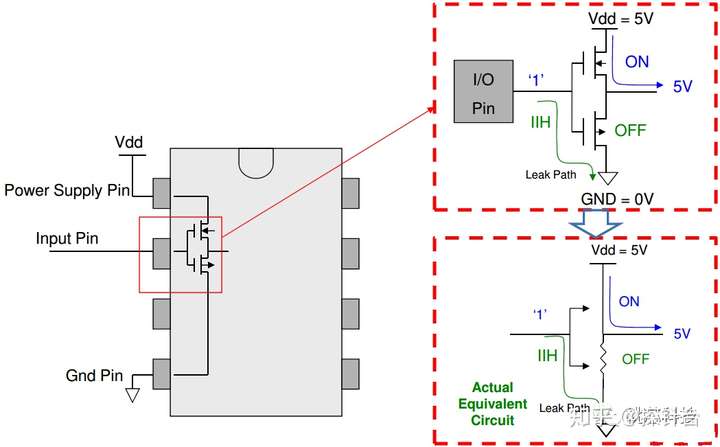

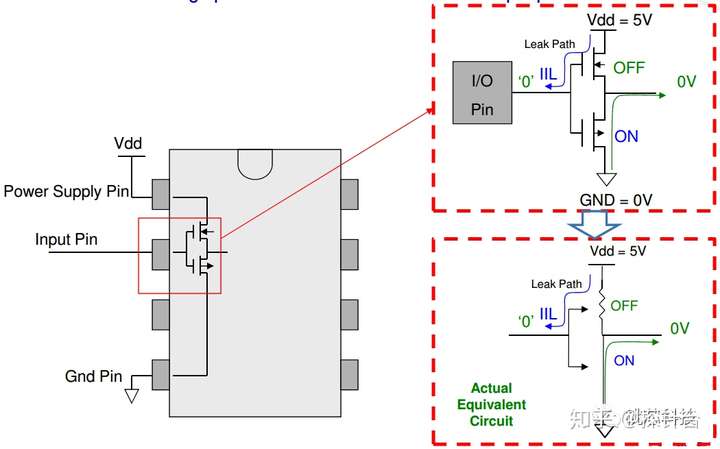

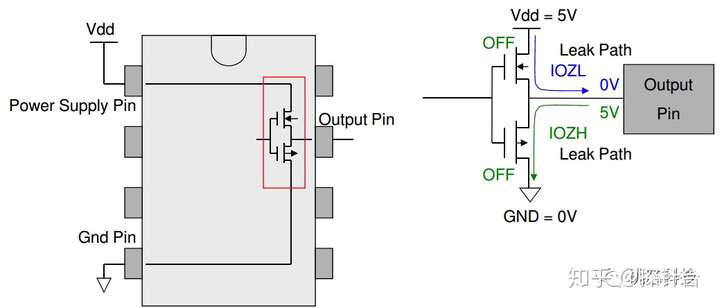

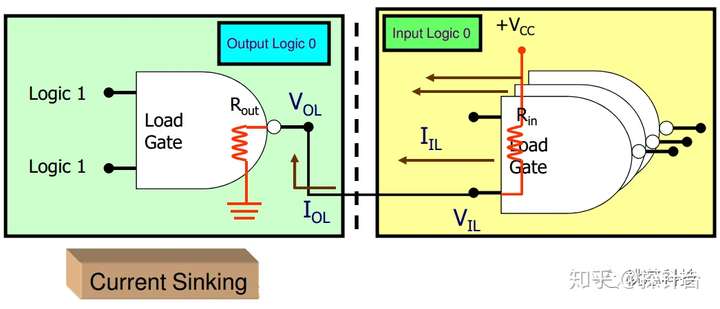

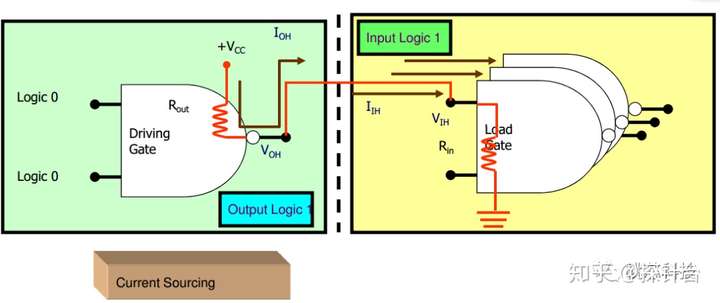

Leakage���� оƬ�ڲ�����ܲ������������״̬����˻����ٻ����һ����©��������Ҫ����©�磬��֤©�����������������ķ�Χ�ڣ�������DZ�ڵ�defect�� Input Leakage Test��IIH and IIL�� IIH�ǵ�оƬ��ij��input pin���趨Ϊ����VIHʱ�������input pin��оƬ��ground֮���©����������ͼ��24����ʾ  ͼ��24�� IIL�ǵ�оƬ��ij��input pin���趨Ϊ����VILʱ����оƬ��VDD �����input pin��֮���©����������ͼ��25����ʾ  ͼ��25�� Output Tristate Leakage Test��IOZL and IOZH�� Tristate��ʾ�������pin�Ǹ���״̬�������ʱ��������pin���е�ѹVDD����ô�����pin��оƬ��ground�ϻ���©�磨IOZH����������pin�ӵأ���ô��оƬ��VDD��������pin��Ҳ����©�磨IOZL����������ͼ��26����ʾ����Щ©����뱣����spec�涨�ķ�Χ�ڣ���ȷ��оƬ������������������DZ�ڵ�defect������  ͼ��26�� Output Logic Low DC Test��VOL/IOL�� VOL��ʾ���ǵ����pinΪ״̬low��ʱ�������ѹ��IOL��ʾ�����ڴ���״̬��������pin�����ĵ������������������Ŀ�Dz��Ե���״̬�µ����pin�Եصĵ����С��������ͼ��27����ʾ��  ͼ��27�� Output Logic High DC Test��VOH/IOH�� VOH��ʾ���ǵ����pinΪ״̬high��ʱ�����С��ѹ��IOH��ʾ�����ڴ���״̬��������pin�����ĵ������������������Ŀ�Dz��Ե���״̬�µ�оƬ��VDD��������pin�ĵ����С��������ͼ��28����ʾ��  ͼ��28�� ����оƬ����Խ��Խ�Ƚ���������ܶ�Խ��Խ�ߣ�оƬ���Եĸ��ӶȺ��Ѷ�Ҳ�ɱ�������������ͨ������ʧЧģʽ�������������ۣ�������һ�»����IJ��Ը���������ǻ�����Ի���źŲ��ԡ�RF���ԡ�DFT���Խ���һЩ̽�֣�лл��

оƬ���Կ��յ����� |  ¥��|

������ 2020-3-17 10:08

¥��|

������ 2020-3-17 10:08

¥��|

������ 2020-3-17 10:08

¥��|

������ 2020-3-17 10:08